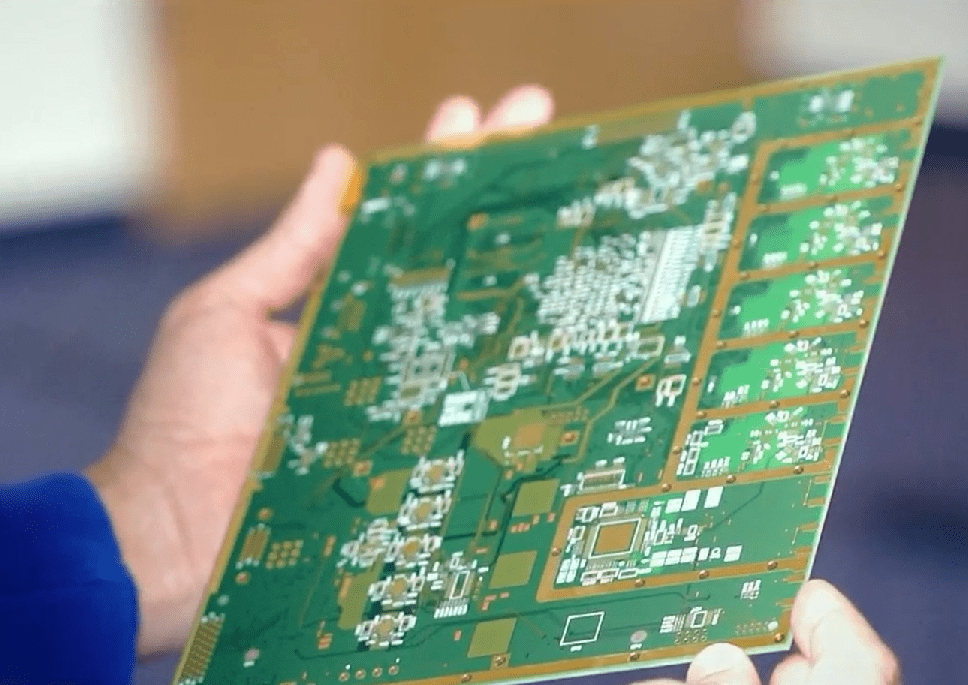

Leiterplattenlayout: Highspeed-Design für PCIe Gen. 4 u. a.

Leiterplattenlayout: Design Challenge 25 Gbit – Highspeed PCB-Design für PCIe Gen. 4 und andere

Steigende Signalübertragungsraten im Multi-Gigabit Bereich erfordern spezielle Designtechniken

Aktuelle neue Schnittstellen-Standards wie PCIexpress 4.0 sowie neue FPGA-Generationen ermöglichen Übertragungsraten bis 2000 Mbit/s. Die Bandbreite des integrierten PCI-Express-Controllers gen 4.0 ermöglicht Bandbreiten von 8-32 Gbit/s.

Auch bei der weit verbreiteten Schnittstelle „Universal Serial Bus“ werden mit USB 3.0 bereits Signalraten von 5 Gbit/s erreicht, mit USB 3.1 ist sogar eine Datenrate von bis zu 10 Gbit/s möglich. Schon für USB 3.0 wird für die 5 Gbit/s eine entsprechende Leitertopolgie benötigt, damit die Übertragung störungsfrei arbeitet.

Der Videostandard „Ultra High Definition Video“ UHD-1 (4k) nutzt eine Datenrate von mehr als 10,2 Gbit/s, weshalb HDMI in der Version 2.0 bis zu 18 Gbit/s liefern kann. Hauptänderung ist die Anhebung der maximalen Bandbreite auf 18 Gbit/s, wodurch Ultra-HD-Inhalte mit 60 Bildern pro Sekunde wiedergegeben werden können. Allerdings wurde übergangsweise auch eine kleinere Datenrate mit der niedrigen Farbquantisierung 8 Bit und 4:2:0 erlaubt, um vorhandene HDMI-1.4-Chips nutzen zu können. Eine weitere Hürde stellt die neue Kopierschutz-Norm HDCP-2.2 dar, die in vollwertigen HDMI-2.0-Anschlüssen vorgeschrieben ist.

Um diese hochfrequenten Signalgeschwindigkeiten störungsfrei auf der Leiterplatte zu übertragen, sind entsprechende Topologien und angepasste Leiterbahnrouting-Methoden erforderlich. Die LVDS-Signalübertragung benötigt eine differentielle Signalführung mit gleicher Leitungslänge für Hin- und Rückleiter. Die Signale erfordern einen Lagenaufbau mit angepasstem Wellenwiderstand (Impedanz). Der Lagenwechsel mittels Vias und Microvias muss besonders beachtet werden, um Impedanzsprünge zu minimieren. Zur Reduzierung der HF-Rückstrompfade sind Stitching Vias sinnvoll. Um Stubs zu vermeiden, sollte manbei langen Highspeed-Leitungen, die über mehrere Lagen geführt werden, die Vias in Backdrilling ausführen. Neben dem Einsatz von entsprechenden Highspeed-Laminaten gibt es weitere neue Routingtechniken, die Störungen entgegenwirken können, wie abgerundete Leiterbahnen oder auch das Zig-zag-Routing.

Man könnte die Aufzählung noch lange mit weiteren Beispielen fortführen. Natürlich bringen die neuen Bauteile und Schnittstellen auch ein komplexeres Powering mit sich. Oft werden 5 – 8 verschiedene Spannungen benötigt, die i. d. R. mit hochgetakteten Linearreglern erzeugt werden. Diese müssen nach festen Regeln designt werden und sind in einem Lagenaufbau für das Powerkonzept entsprechend einzuplanen. Die Referenzflächen für impedanzbehaftete Signale müssen möglichst homogen sein und die Vias dürfen den HF-Rückstromweg möglichst wenig behindern. Das ist gerade bei hochpoligen Finepitchsteckern, die mitten auf der Leiterplatte liegen, oft eine Herausforderung.

Bei komplexen Multilayern wird es zunehmend erforderlich, die Homogenität der Versorgungsflächen, die für die zuverlässige Signalübertragung und die EMV-Festigkeit wichtig sind, mittels „Power Integrity Simulation“ zu überprüfen.

Speicherdichten erhöhen sich zunehmend, DDR4

Die DDR-SDRAM-Technologie hat ihre vierte Generation erreicht;DDR4-SDRAM-Schnittstellen erreichen eine maximale Datenrate von 3,2 Gbit/s (d.h. eine Taktrate von 1,6 GHz). Beim Design gibt es vier wichtige Anforderungen für die Platzierung und das Routing von DDR4-SDRAM-Schnittstellen mit Multi-Gigabit-Übertragung. Diese großen Herausforderungen umfassen die Routingtopologie und das Terminierungssystem für die Netze mit mehreren Speichern, das eine Routing-Technik mit geringem Übersprechen erfordert. Es werden spezielle Designmethoden eingesetzt, um die Impedanzsprünge aufgrund von Durchkontaktierungen zu minimieren.

Die Routing-Technik für mehrere Speicherbausteine erzeugt mit der herkömmlichen Art von Routing mit Baumtopologie sogenannte „Trace Stubs“, die die Signalintegrität des Übertragungskanals verschlechtern. Die Wirkung von Stubs ist unten in der Formel erläutert, nach der die Resonanzfrequenz oder die Bandbreite der Übertragungsleitung umgekehrt proportional ist zur Stublänge. In der herkömmlichen Baumtopologie führt der „Trace Stub“ mit der Zunahme der Anzahl von Speichern zu unerwünschten Verlängerungen, die Störungen hervorrufen.

- f o = Resonanzfrequenz (Hz)

- c = Lichtgeschwindigkeit (1.18×10 10 Zoll/s)

- stub_length in inches

- Dk = Dielektrizitätskonstante

Der Einsatz von verlustarmen Materialien, sogenannte „High speed laminate“ wie Megtron (Panasonic) oder I-Tera (Isola), wird ebenso erforderlich wie ein „backdrilling“ von durchgehenden Vias. Für das Routing der Leiterbahnen ist ein Tuning der Leitungslängen erforderlich und das mit sehr engen Toleranzen. Ohne diese Designmaßnahmen ist eine zuverlässige Signalübertragung nicht mehr möglich.

Zur Steigerung der Zuverlässigkeit und auch zum Qualitätsnachweis der Gigbit-Übertragungssysteme setzt GED das SI-Simulationswerkzeug Hyperlynx von Siemens (ehem. Mentor Graphics) ein. Damit lässt sich die Signalintegrität in Form der Augendiagramme simulieren. Mittels „Presimulation“ kann bereits bei der Planung der Topologie des Multilayers eine Prüfung der berechneten Impedanzwerte vorgenommen werden.

Bei der Planung des HDI-Multilayers sind i.d.R. mehrere verschiedene Impedanzen gefordert mit einer Toleranz von max. 10% und 0,5 dB Einfügungsdämpfung. Der Lagenaufbau, Material mit niedriger Dielektrizitätskonstante (DK) und die Viatopologie bilden dafür die Basis. Eine saubere Leiterführung und ein optimaler Längenausgleich der Differential-Pair-Leitungen beim Routing stellen die Einhaltung der Toleranzen sicher.

Höhere Verbindungsdichte durch Bauteile-Miniaturisierung und steigende Anschlussanzahlen

Neue Bauteilegehäuse werden zunehmend kleiner und haben höhere Anschlusszahlen. LQFP, QFN oder MLP-Gehäusebauformen haben bis ca. 100 Anschlüsse bei einer Kantenlänge um die 5 mm. µBGA oder CSP-Bauteile erreichen bis weit über 1.000 Anschlüsse. Diskrete Bauteile gibt es in winzigen Gehäusebauformen wie 0201, Micro-MELF oder SOT-883 mit 3 Anschlüssen und mit einer Größe von nur 1 x 0,6 x 0,5 mm. Damit lassen sich inzwischen Miniaturisierungsgrade erzielen, die ehemals nur mit COB-Technik, also mit ungehäusten Bauteilen, erzielt wurden. Es gibt heute moderne FPGAS wie Kintex 7™ von XILINX, die bis zu 1.156 Anschlüsse (I/O´s) haben, oder auch ASIC-Bauteile mit über 2.500 Anschlüssen, mit Pitchmaßen bis runter auf 0,4 mm.

So genannte HDI-(High-Density-Interconnection) Leiterplattentechnologien, die eine höhere Verbindungsdichte durch Einsatz von Microvias (150 µm) und Burried Vias in Verbindung mit feinen Leiterstrukturen unter 150 µm haben, können die Verbindungsdichte einer Leiterplatte signifikant steigern und ermöglichen den Anschluss von Bauteilen mit hoher Pin-Dichte. Je nach Größe und Anforderung werden heute auch Leiterstrukturen von 50 µm in Serie produziert. Künftig wird für Pitchmaße von nur 0,3 mm eine Leiterbreite von, zumindest partiell, nur 30 µm benötigt.

GED hat in den letzten Jahren viele Highspeed-Designs erfolgreich umgesetzt, die auf Anhieb funktioniert haben. Grundlage dafür sind Kenntnisse und Erfahrungen der PCB-Designer bei GED, die eine umfangreiche Planung der Leiterplattentechnologie und der Impedanzen vornehmen und viel Know-how in eine optimale Bauteileplatzierung stecken. Sofern gewünscht, wird eine Signal- und Powerintegritäts-Simulation durchgeführt. Der Rest ist dann gekonnte Handarbeit, denn GED nutz keine Autorouter, sondern verlegt alle Leitungen manuell. Dabei hilft lediglich ein interaktiver Router, den die modernen, leistungsstarken CAD-Werkzeuge wie beim Siemens XPEDITION CAD bieten. Durch die enge Zusammenarbeit mit den Leiterplattenherstellern werden die Material- und dfm Anforderungen abgestimmt, was letztlich zum First Time Right beiträgt.

GED unterstützt Sie mit über 35 Jahren Erfahrung und Spezialkenntnissen, setzt modernste CAD- und Simulationstools ein und verfügt über ein erfahrenes Spezialistenteam für die verschiedenen Aufgabenbereiche, auch bei komplexen und zeitkritischen Projekten.

Sprechen Sie mit uns über Ihre Anforderungen!

Newsletter-Teaser:

Neue Schnittstellen-Standards wie PCIexpress 4.0 sowie neue FPGA-Generationen ermöglichen Übertragungsraten bis 2000 Mbit/s. Die Herausforderung: Um diese hochfrequenten Signalgeschwindigkeiten störungsfrei auf der Leiterplatte zu übertragen, sind entsprechende Topologien und angepasste Leiterbahnrouting-Methoden erforderlich.

Sensorik: GED und accensors vereinen Know-how

Partner kooperieren bei Kundenprojekten und Zukunftsthemen im Bereich Sensorik

Pressemitteilung

Espelkamp/Ruppichteroth, 8. November 2022. Blick in Zukunftsthemen der Elektronik: Foliensensor-Entwickler accensors und Elektronik-Spezialist GED vereinen ihr Know-how in einer strategischen Partnerschaft. Ziel der Bündelung von Kompetenzen ist das Entwickeln neuartiger und innovativer Sensorsysteme, welche unter anderem in der Medizintechnik Anwendung finden können. Mit der Fachkenntnis und Erfahrung in der Sensorik und Elektronik können die Partner zusammen sowohl Kundenprojekte als auch Eigenentwicklungen schneller und effizienter umsetzen und zur Marktreife bringen. Doch auch Trends und Themen der Elektronikbranche sollen gemeinsam beobachtet, analysiert und entwickelt werden.

„Durch die Zusammenarbeit mit GED schaffen wir einen doppelten Mehrwert“, betont Eike Wilhelm Kottkamp, Geschäftsführer von accensors. „Zum einen verbinden wir accensors enger mit einem professionellen Elektronik-Entwicklungsunternehmen und werden so die Qualität, die Expertise und das Zuliefernetzwerk im Bereich Auswerteelektronik ausbauen. Zum anderen gibt uns die Partnerschaft weitere Freiheiten in unserer Fachdisziplin – die Entwicklung und Produktion von Foliensensoren.“

„Wir freuen uns über die vertiefte, langfristige Partnerschaft mit accensors,“ sagt GED-Geschäftsführer Hanno Platz. „Wenn Professionalität und Innovation zusammentreffen, dann werden starke Synergien freigesetzt. Gemeinsam mit accensors können wir unser Leistungsspektrum deutlich erweitern und sehen ein enormes Entwicklungs- und Marktpotenzial. Von der Partnerschaft mit einem ausgewiesenen Sensorspezialisten werden eigene Produktideen profitieren. Vor allem aber können wir durch unsere Zusammenarbeit den Kunden besonders effektive Entwicklungsprozesse bieten, die zu ausgefeilten, kostenoptimalen Lösungen führen.“

Mit dem Start der Partnerschaft wird eines ihrer bisherigen gemeinsamen Projekte auf die nächste Entwicklungsstufe gehoben. In engster Zusammenarbeit haben die Unternehmen eine Smart-Patch-Plattform (Smart Patch, intelligentes Pflaster) entwickelt, um intelligente Sensorik auf die Haut zu bringen. Hier gehen nun accensors und GED die nächsten Schritte zu einem ersten Medizinprodukt. Dabei umfasst die Kooperation auch das anspruchsvolle Zulassungsverfahren nach der MDR (Medical Device Regulation). Auch bei der Identifizierung und Bewertung strategischer Wachstumsthemen werden GED und accensors zukünftig sehr eng zusammenarbeiten. Ein Beispiel ist der Bereich Edge-Computing. Hier teilen die beiden Partnerunternehmen die Überzeugung, dass Sensor-Netze mit Datenverarbeitung an der Netzwerkperipherie eine stark zunehmende Bedeutung für die Digitalisierung in Wirtschaft, Gesellschaft und insbesondere für die Industrie 4.0 haben.

Über accensors

accensors GmbH, Espelkamp, ist ein Pionier für Foliensensoren, Folienaktuatoren und Folienemittern. Immer öfter nutzen die unterschiedlichsten Branchen spezifische Sensoren, um permanente Zustandsüberwachungen zu ermöglichen. accensors entwickelt dafür neuartige flexible sowie bauteilangepasste und designfreie Foliensensoren. Die hier entstehenden Detektoren, welche bspw. den ph-Wert im Urin oder den Anpressdruck einer Schraube überwachen, sollen die Industrie 4.0, das Internet of Things oder auch Wearables noch intelligenter gestalten – dies ist das Ziel von accensors.

Kontakt: info@accensors.com Internet: https://accensors.com/

Über GED

Die GED Gesellschaft für Elektronik und Design mbH (Ruppichteroth) ist seit über 35 Jahren in der Entwicklung und Fertigung von Elektronikkomponenten und -komplettlösungen aktiv. Zum Leistungsportfolio des inhabergeführten Unternehmens gehören u. a. die Beratung und Konzeptionierung sowie die Entwicklung von individuellen Lösungen für kundenspezifische elektronische Schaltungen und Verbindungstechnologien. Anwendung finden die Produkte in den unterschiedlichsten Branchen wie Automotive, Medizintechnik- und Industrieproduktion. GED hat zudem ein eigenes Medizinprodukt entwickelt und ist als Entwicklungs- und Fertigungsunternehmen nach ISO 13485 zertifiziert.

Kontakt: h.platz@ged-pcb-mcm.de Internet: www.ged-pcb-mcm.de

Diese Pressemitteilung als Download.

Schwindeltherapie-Lösung von GED überzeugt HNO-Fachleute

Auf der 55. Fortbildungsveranstaltung für HNO-Ärzte Ende Oktober 2022 in Mannheim hat GED das innovative Schwindeltherapie und -diagnoseprodukt EQUIVert dem Fachpublikum vorgestellt. Am Ausstellungsstand konnte GED dazu viele gute Gespräche mit Fachärztinnen und -ärzten führen – ein großer Erfolg für EQUIVert und das Unternehmen. Dabei gab es viel positives Feedback für die wegweisende Lösung und ihren Nutzen in der Diagnostik und Therapie.

Basis der in Deutschland entwickelten und hergestellten Geräte sind eine stark miniaturisierte Elektronik von GED mit Gyro- und Beschleunigungssensor, Audioelektronik für akustisches Biofeedback sowie Sprachansagen und Gestensteuerung für die Bedienung. Mehr zu EQUIVert und den Produkten EQUIMedi und EQUIFit erfahren Sie hier.

Der HNO-Fortbildungskongress wird jährlich von der Deutschen Fortbildungsgesellschaft der Hals-Nasen-Ohrenärzte mbH durchgeführt, alleiniger Gesellschafter ist der Deutsche Berufsverband der Hals-Nasen-Ohrenärzte e. V.

Der siebte Sinn auf der DigitalXchange 2022: Skalierbare KI-Mikrosensorik zur Maschinenüberwachung

GED Teamtraining: PCB-Design und Entspannung

Vom 17. bis 19. Mai 2022 war es soweit: GED konnte nach langer Corona-Auszeit endlich wieder einmal in die bewährte Teamschulung gehen. Die Veranstaltung startete mit einem Tagesseminar: „Best Practices with Colleagues“. Alle Mitarbeiter zeigten aus ihren technisch anspruchsvollsten PCB-Designs der letzten zwei Jahre die von ihnen angewandten Designstrategien, die dann in der Runde diskutiert wurden.

Die vorgestellten Projekte deckten das gesamte LP-AVT-Portfolio ab:

- Highspeed und HDI-PCB-Design: Wie sehen eine optimale Anordnung und der Lagenaufbau für eine Leiterplatte mit sechs Stück DDR4-Speichern auf möglichst kleiner Fläche aus, bei optimalem Längenausgleich von max. 0,1 mm? Ein optimales Ergebnis für erreicht GED, weil für das Längenmatching der Leiterbahnen, die Längen im Chip mit betrachtet werden und der Abgleich nach der Signallaufzeit vorgenommen wird. Die Lösung überzeugte: Der Kunde gab die Rückmeldung, dass aufgrund des mustergültigen Längenabgleichs der differentiellen Leiterbahnen das Design von GED optimale Ergebnisse erzielte. Grundlage ist eine ideale Anordnung der Bauteile und zum Abgleich wurden nicht die maximalen Leiterlängen, sondern die Signallaufzeiten verwendet. Auch die Leiterlängen im Chip wurden berücksichtigt, was bei einer Längentoleranz von höchstens 0,1 mm eine wichtige Rolle spielt.

- HDI-PCB-Design: Wie ist der günstigste Lagenaufbau und welche Microvicas verwende ich für einen 196-poligen BGA mit Pitch 0,5 mm? Aktuell ist ein Design mit Pitch von nur 0,3 mm für ein µBGA in Arbeit und es gibt inzwischen Bauteile mit Pitchmaßen von nur 0,2 und 0,1 mm.

- Powerelektronik: Mit welchem LP-Entwärmungskonzept gelingt die optimale Wärmeabfuhr auf einem 20 kW-DC/DC-Wandler mit SIC-MOSFETs bei einer Leistung von 50 Watt pro Bauteil – Ansteuerung 100 kHz Spannung 1,5 KV?

- Powerelektronik – Entwicklung Hardware, Software und PCB-Design: Konzeption, Gerätedesign eines 19- Zoll-Racks mit fünf Typen Leiterplatten; mechanischer Aufbau mit Solid Works, verbunden mit Altium Designer für das PCB-Design mit vier Powerkarten 12/24 Volt à 50 Ampere. Die gesamte Mechanik des ersten Entwurfs konnte durch das 3D-Co-Design ohne Änderungen in die Serienfertigung übernommen werden.

- 3D-Elektronik-Design: In-Ear-Produkt mit hochpoligem BGAs auf einer 6-lagen Starrflex-Leiterplatte in Fingernagelgröße, mit BGAs Pitch 0,4 mm und extremer Packungsdichte.

- Entwicklung Medizinprodukt, Klasse 2B: Hardware, Software und PCB-Design: Lade- und Überwachungseinheit für drei Batteriepacks, Steuerkarte für zwei Displays, Sensoren, Pumpen, vier Mikrocontroller, die auf einer Main- und vier Subleiterplatten verteilt sind. Das hierarchische Schaltplandesign ermöglichte es, hier ein optimales Testkonzept für die gesamte Schaltung zu entwickeln.

Konsens der Expertenrunde am ersten Tag war, dass gerade bei den sogenannten Advanced Technology Designs, wie Highspeed, Power oder High-Density u. a., eine „Designreserve“ mit vorgesehen wird. Sowohl auf der funktionalen Seite als auch bei der Produktion gibt es Toleranzen zu berücksichtigen. Gerade Spezialthemen wie Material- und Lagenaufbau für die Impedanzanpassung für hohe Taktraten, Load-Dump-Belastungen in Hochstromanwendungen oder CAF-Effekte im Material u.v.a.m. erfordern neben der sicheren Schaltungsauslegung auch immer ein „sauberes“ PCB-Design.

Sturm auf die Burg

Nach so viel Projekt- und Fachdiskussion boten am folgenden Tag die Wanderung und die Erstürmung der Burgruine Stadt Blankenberg die verdiente Entspannung. Die ehemals kleinste Stadt Deutschlands gehört heute zur Stadt Hennef. Bei bestem Wetter wurde das GED-Team mit einem herrlichen Ausblick nach Siegburg mit der Abtei Michaelsberg und sogar weiter bis nach Köln belohnt. Der Ausflug war für Mitarbeiter aus dem Homeoffice eine hochwillkommene Gelegenheit, endlich ihre Kolleginnen und Kollegen wiederzutreffen oder kennenzulernen.

Am dritten Tag waren „Trainings on the Job“ am CAD-System angesetzt. Die erfahrenen Kollegen verrieten Tipps und Tricks für die Xpedition und Altium CAD-Tools. Neuigkeiten von der Siemens EDA (Mentor) User2User Conference, die gerade eine Woche vorher in München stattgefunden hatte, wurden den Kollegen taufrisch weitervermittelt.

Das Teamtraining 2022 zeigte einmal mehr, dass diese entspannte Art des Wissensaustauschs neben dem Lernen von den Erfahrungen anderer auch das Verständnis der Kolleginnen und Kollegen füreinander fördert. Alle waren sich einig: Drei erlebnisreiche und informative Tage zur Stärkung des Teams, die im nächsten Jahr fortgeführt werden.

GED beteiligt sich aktiv am Innovation Hub Bergisches RheinLand

Seit Januar 2022 ist GED Mitglied des regionalen Technologienetzwerks Innovation Hub Bergisches RheinLand in Gummersbach. Das Unternehmen unterstützt den Innovation Hub im Handlungsfeld Predictive Maintenance mit dem GED-SensorNode: An einem Demonstrator mit verschleißanfälligen Maschinenteilen wird die sensorische Erfassung, Verarbeitung und Weiterleitung von Daten für die vorausschauende Wartung aufgezeigt und optimiert. Darüber hinaus hat GED beschlossen, künftig zusammen mit dem Projektpartner des Innovation Hub, der TH Köln, gemeinsame Forschungsprojekte für die KI-Auswertung von Sensordaten durchzuführen.

„Wir sind begeistert, dass wir für unseren leistungsfähigen IoT-Multisensorbaukasten beim Innovation Hub Bergisches Rheinland eine ideale Umgebung für Anwendungsszenarien und Weiterentwicklungen gefunden haben“, sagt GED-Geschäftsführer Hanno Platz. „So können wir für den Anlagen- und Maschinenbau neue, smarte Multisensor-Lösungen im Rahmen von Industrie 4.0 kreieren. Gemeinsam mit der TH Köln wollen wir mittels erweiterter Algorithmen und Künstlicher Intelligenz wesentliche Fortschritte in der Datenanalyse schaffen. Unser völlig neu entwickeltes SensorNode-Konzept bietet dafür gerade im Bereich Predictive Maintenance eine optimale Basis.“

Sensorprojekte im Fokus

Zentrum des Innovation Hub Bergisches RheinLand ist die Halle 51 auf dem Steinmüllergelände in direkter Nachbarschaft zur TH-Köln am Campus Gummersbach. Dieser Neubau wird unter anderem mit interessanten Maschinen ausgestattet, an denen Sensorerweiterungen für das zukunftsrelevante Thema „Predictive Maintenance“ adaptiert werden. Dazu zählen CNC-Maschinen, Spritzgussmaschinen, 3D-Drucker, Roboter usw. und ein Maschinen-Demonstratoraufbau. Der Elektronikspezialist GED setzt darauf, sich hier an vielen spannenden Sensorprojekte beteiligen zu können, um das weite Leistungsspektrum des Unternehmens im regionalen Umfeld aufzuzeigen.

Zentrum des Innovation Hub Bergisches RheinLand ist die Halle 51 auf dem Steinmüllergelände in direkter Nachbarschaft zur TH-Köln am Campus Gummersbach. Dieser Neubau wird unter anderem mit interessanten Maschinen ausgestattet, an denen Sensorerweiterungen für das zukunftsrelevante Thema „Predictive Maintenance“ adaptiert werden. Dazu zählen CNC-Maschinen, Spritzgussmaschinen, 3D-Drucker, Roboter usw. und ein Maschinen-Demonstratoraufbau. Der Elektronikspezialist GED setzt darauf, sich hier an vielen spannenden Sensorprojekte beteiligen zu können, um das weite Leistungsspektrum des Unternehmens im regionalen Umfeld aufzuzeigen.

Über den Innovation Hub

Der Innovation Hub Bergisches RheinLand versteht sich als Knotenpunkt zwischen Unternehmen und wissenschaftlichen Einrichtungen in der Region Bergisches Land/Rheinland. Durch einen „Open-Innovation-Ansatz“ schafft er Forschungsmöglichkeiten im Kontext der Digitalisierung, die Beteiligte allein nur schwer und mit deutlich größerem Aufwand realisieren könnten. Das Team setzt sich aus dem Verein und der TH Köln zusammen. Insgesamt haben sich 30 Mitarbeiterinnen und Mitarbeiter, darunter sieben Professoren und sechs wissenschaftliche Mitarbeiter, dem Ziel der Digitalisierung von kleinen bis großen mittelständisches Unternehmen aus der Region verschrieben. Mitglieder sind beispielsweise ABUS Kransysteme GmbH, Ralf Bohle GmbH (Schwalbe-Fahrradreifen), NetCologne Gesellschaft für Telekommunikation GmbH und SARSTEDT AG & Co. KG.

Der InnoHub wird, zusammen mit der TH Köln und dem Innovation Hub Bergisches RheinLand e.V., unter dem Projektnamen „Regio.NRW – Innovation Hub Bergisches RheinLand“ durch den Europäischen Fonds für regionale Entwicklung EFRE gefördert.

Purchasing by Design: Strategie gegen Beschaffungsprobleme bei Neuentwicklungen

Auswahl und Bestellung in der Design- und Entwicklungsphase – frühzeitige Planung mit angepasstem Entwicklungsprozess zur Beschaffung elektronischer Bauteile

Die Beschaffungssituation in der Elektronikbranche hat sich in 2021 weltweit derart verschärft, dass Lieferzeiten von 40-100 Wochen für unterschiedlichste Bauteile fast an der Tagesordnung sind. Dabei sind nicht nur Microcontroller betroffen, sondern auch Standardbauteile wie Kondensatoren oder Stecker. Auch bei den Rohstoffen für Leiterplatten oder Kunststoffen sind inzwischen erhebliche Verknappungen und damit auch Preissteigerungen zu verzeichnen.

Bereits 2019 hatten wir in unserem Newsletter berichtet, dass durch internationale Entwicklungen das Thema Bauteile-Obsoleszenz in den nächsten Jahren noch deutlich an Brisanz zulegt: Neue Megatrends in der Elektronik benötigen erheblich mehr Bauteile durch höhere Stückzahlen, steigende Funktionalität und kürzere Lebenszyklen.

Aktuell ist die globale Corona-Pandemie nicht die einzige Ursache der Lieferprobleme. Gleich mehrere Gründe haben seit 2020 mit steigender Tendenz die Lage verschärft:

– Feuer und Hitze in Asien, mehrere Werke für verschiedene Rohstoffe waren durch Brände betroffen

– Kältewelle in den USA (Florida, Texas), Ausfall von Chipwerken, Stromausfälle

– Logistikprobleme für See und Luftfracht, Transportkosten von China steigen um Faktor 5-10

– Globaler Rohstoffmangel bei Kupfer, Harzen, Kunststoffen u.v.a.m.

Wenn kleine Ereignisse hinzukommen, wie der Unfall der „Ever Given“ auf dem Suezkanal, sind die Auswirkungen direkt spürbar. Immerhin hat ein modernes Containerschiff Ladekapazitäten von über 20.000 Containern. Aber auch der Handelskonflikt zwischen China und dem Westen wird sich künftig noch weiter auswirken. Die Tendenz für das neue Jahr 2022 sieht daher leider nicht gut aus, Allokationen und Preissteigerungen werden noch für das gesamte Jahr und darüber hinaus bestehen bleiben. Demgegenüber steht ein Wachstum im Halbleitermarkt von über 25 %, dass die World Trade Statistics (WSTS) im August 2021 prognostiziert hat.

Welche Strategien können insbesondere bei neuen Produktentwicklungen helfen?

GED bietet den Kunden im Rahmen der Design- und Entwicklungsaufträge auch den Service der Baugruppenfertigung für Muster und Kleinserien, inklusive der Materialbeschaffung. Der besondere Vorteil liegt darin, dass sich ein Team mit speziellen Elektronik- und Marktkenntnissen um die Beschaffung kümmert, auch um die sogenannten „schwerbeschaffbaren Bauteile“. In der aktuell angespannten Lage helfen aber leider auch nicht mehr die guten Quellen oder der Einkauf über zertifizierte Broker.

Das Unternehmen hat deshalb auf die Situation mit einer angepassten Strategie reagiert und gute Erfahrungen gemacht. Die Beschaffung wird bereits parallel zum Designprozess durchgeführt. Bei der Auswahl der Bauteile recherchieren die Entwickler die Verfügbarkeit – die Bestellung muss dann natürlich möglichst zeitnah erfolgen. Das ist zwar aufwendig und zieht teilweise auch mehrere Bestellvorgänge nach sich. Idealerweise liegen dann aber zum Designende bereits die Bauteile für die Bestückung bereit. GED empfiehlt den Kunden, die Materialbeschaffung gleich mit dem Designauftrag zu platzieren. Wir unterstützen sie dann schon beim „Design in“ mit der Beschaffung des Materials.

Hier die Vorschläge aus dem GED-Newsletter 2019, die heute um so mehr gelten:

Beschaffung mit Weitsicht

Das bedeutet, in der Entwicklungs- und Designphase ist es zukünftig wichtiger denn je, besondere Vorkehrungen im Hinblick auf Obsoleszenz und lange Lieferzeiten zu treffen. Natürlich wäre die erste Forderung stets, eine Second Source zu bestimmen. Das ist leider nicht immer möglich. Dagegen sind Regelungen, wie nur ein bestimmtes Fabrikat für Keramikkondensatoren festzuschreiben, sehr eingrenzend und gefährlich. Der Einsatz von speziellen Modulen, z. B. Powermodule, ist in der Regel auch damit verbunden, dass ausschließlich Bauteile von einem Hersteller verwendet werden müssen.

Aber womit fängt die Lösung des Problems dann an? Bei der Bauteile-Auswahl steht der Entwickler vor einer großen Anzahl an Optionen. Ein Beispiel: Bei einem MLLC mit 100 nF und Bauform 0402 bietet ein bekannter Distributor derzeit schon einmal 374 Möglichkeiten an. Lässt man hier den Entwickler in der Entscheidung freie Hand, entstehen schnell unnötige Einschränkungen. Deshalb empfiehlt sich bei der Beschaffung und Festlegung neuer Bauteile eine klare strategische Vorgabe oder eine Prüfung durch entsprechende Abstimmung und Zusammenarbeit mit der Einkaufsabteilung. Bei der ausgelagerten Fertigung über EMS-Dienstleister ist es wichtig, deren Lager zu berücksichtigen und/oder zu kennzeichnen, welche Bauteile nicht auf einen Typen oder Hersteller festgelegt sind. Ausgewählte Bauteile sollten eindeutig identifizierbar sein. Neben der Festlegung der elektrischen Werte und der Bauform des Bauteils sind auch Angaben über die Spannungs- und Toleranzklasse relevant.

Welche Vorgehensweise ist sinnvoll und welche Angaben sollte die Stückliste/BOM enthalten?

Gezielte Auswahl neuer Bauteile:

- Analyse zur Produktdefinition in der Vorprüfung (PDR), Critical Design Review (CDR) etc.

- Klassifizierung der eindeutigen, zweideutigen und fehlerhaften Teileidentifikationen/-beschreibungen

- Identifizierung der Ursachen für unzureichende Bauteilebeschreibungen

- Alternative Bauteile, Second Source

Minimal Angaben für eine exakte Bauteile-Identifikation

- Name und/oder Beschreibung

- Teilenummer(n) aus dem OEM(s)/OCM(s)

Namen der OEM(s)/OCM(s) - Hersteller-Code (CAGE = Commercial-and-Government-Entity-Code)

- NSN-/NATO-Nummer (National Stock Number oder NATO Stock Number)

- Anzahl der benötigten Teile pro Baugruppe

Darüber hinaus sollte man folgende Punkte generell berücksichtigen:

- Verfügbarkeit der ausgewählten Bauteile prüfen, insbesondere bei neuen Typen

- Abkündigungen und „End of Life“ (EOL) und „Part Change Notification“ (PCN) prüfen

- Immer A-Bauteile wie Controller, Speicher, Stecker, Display usw. auf Lieferzeiten prüfen

- Auch C-Bauteile frühzeitig auf Lieferfähigkeit prüfen

- Frühe Abstimmung mit dem Baugruppenfertiger, BOM-Analyse

- Materialbeschaffung für Serienstart früher planen und Material früher bestellen

- Regelmäßige Überwachung der Materialien

Kurz gesagt, es empfiehlt sich, weitsichtig zu denken und zu planen:

- Ersatztypen festlegen, Second Source in die BOM aufnehmen.

- Bei kritischen Bauteilen alternative Gehäuseformen im Layout vorsehen.

- Frühzeitige Serienplanung und Materialbeschaffung, ggf. Lagermenge anlegen.

- Vorsicht bei Bauteilen wie Displays, MEMS Mikro, Powermodule usw., Material optional selbst bevorraten.

- Ggf. „alternative shapes“ für kritische Bauteile vorsehen.

- Je größer die Serie, desto wichtiger ist eine frühzeitige Planung.

- Bei Ersatzbeschaffung über Broker oder Refurbished-Anbietern ist Vorsicht geboten. Hier empfehlen wir das Röntgen und einen elektrischen Qualifizierungs- oder Vergleichstest.

GED verfügt aus mehr als 30 Jahren Erfahrung in Entwicklung und Design über Designstrategien, die bestimmte Risiken deutlich minimieren können. Bereits beim Leiterplattendesign kann man mit vielen kleinen Maßnahmen dafür sorgen, dass alternative oder ähnliche Bauteile eingesetzt werden können. Das reicht vom alternativen Footprint bis hin zur weitsichtigen Platzierung der Bauteile und anderen Design-Maßnahmen.

Bauteil ist nur im anderen Gehäuse lieferbar?

Für die Möglichkeit alternativer Gehäuse ohne ein Redesign auf der Leiterplatte entwickelt GED sogenannte Interposer-Module. Die Umsetzung des Footprints wird auf einer kleinen HDI-Leiterplatte vorgenommen. Optimal dafür ist, wenn das alternative Bauteil eine kleinere Bauform hat. Auf dem Modul kann ggf. auch noch eine Schaltungsanpassung mit aufgebracht werden. Ist das Bauteile größer, kann das alternative Bauteile auf ein Pinheader montiert werden, der über die anderen Bauteile der Leiterplatte ragt.

Fazit:

Die gesamte Elektronikbranche steht vor akuten und massiven Herausforderungen in der Supply Chain. Denn hier stehen nicht mehr die Preisänderungen im Vordergrund, sondern dass es überhaupt geliefert werden kann. Dabei ist die beste Strategie, frühzeitig zu planen und zu beschaffen. Sprechen Sie mit Ihren Lieferanten für Ihre Entwicklungsprojekte und Bedarfe im Jahr 2022 am besten jetzt. Wir unterstützen Sie gern!

Netzwerk 3D-Elektronik: Wegweisende Projekte und Neustart

Am 30. November 2021 traf sich das 2018 vom FED initiierte ZIM-Netzwerk 3D-Elektronik zum siebten Mal. Nach nun drei Jahren geförderte Laufzeit beschlossen die Mitglieder aufgrund des Erfolges, ihr Unternehmen und Forschung übergreifendes Technologie-Netzwerk jetzt offen weiterzuführen.

Starke Innovationsprojekte vorgestellt

Die ursprünglich an der Ruhr Uni Bochum geplante Präsenzveranstaltung wurde kurzfristig digital durchgeführt. Die Mitglieder präsentierten die Ergebnisse der aus dem Netzwerk heraus initiierten FuE-Projekte. Die mit öffentlichen Mitteln unterstützen ZIM-Projekte (ZIM, Zentrales Innovationsprogramm Mittelstand) verfolgen das Ziel, elektronische Baugruppen komplexer, hochintegrierter, kosten- und energieeffizienter sowie zugleich platzsparender umzusetzen. Beispielsweise entwickelt die Firma metak innerhalb des ZIM-Projekts „BauteilBett“ ein neues Verfahren zur Fertigung von elektronischen Freiformbauteilen. Damit können elektronische Komponenten erstmalig gezielt in Spritzgussteile integriert werden.

Die van Rickelen GmbH sowie das Fraunhofer IMS entwickelten im gemeinsamen FuE-Vorhaben „noKat“ einen neuen optischen Näherungssensor, der in der Lage ist, Menschen mit Hilfe künstlicher Intelligenz zu erkennen. So kann die aktuell sehr hohe Anzahl unerwünschter Erkennungen mit klassischen Näherungssensoren, etwa durch Tiere oder Wind, deutlich reduziert werden. Da es sich zudem um ein Microcontroller-basiertes Embedded-System handelt, werden die Daten lokal verarbeitet und gelangen nicht nach außen. Das Projekt wurde bereits erfolgreich abgeschlossen. Zudem ist ein Folgeprojekt in Planung.

Ein weiteres technisch spannendes Projekt ist der IoT-Sensorbaukasten SensorNode mit Energy Harvesting über Bewegungsenergie (Vibration), den GED entwickelt hat:

GED-SensorNode – modulares 3D-Elektronik-Sensorsystem

- Mikrocontroller-Modul: 32 bit ARM-Cortex M4, für sensor data preprocessing und sensor control,

Bluetooth Funk BLE 5, 50-pin Sensor Bus, Plug&Play

Bluetooth Funk BLE 5, 50-pin Sensor Bus, Plug&Play - Kraftmess-Modul, 24 bit

- Motion-Modul

- Datalogger-Modul

- Power-Modul für Akku und Energy-Harvesting

- Modul-Baugröße ca. 15 x 18 x 14 mm

Fünf Partner starten neues gefördertes AVT-Projekt

Das Netzwerk konnte zum Abschluss der Förderphase noch einen positiven Entscheid zu einem größeren Projektantrag mit einem Fördervolumen von 1,8 Mio. Euro verbuchen. Über das Programm „KMU-innovativ“ des BMBF startet ein Konsortium aus fünf Partnern (NanoWired GmbH, Becker & Müller Schaltungsdruck GmbH, GED mbH, Huber Automotive GmbH, TU Dresden) eine Entwicklungskooperation zur industriellen Umsetzung einer neuen AVT auf Basis des patentierten Verfahrens „KlettWelding“ von NanoWired. An zwei Demonstratorprojekten sollen optimierte Verbindungslösungen für hohe Signalübertragungsraten bis 20 GHz und hohe Leistungen bis 20 kW auf Basis der neuen Aufbau- und Verbindungstechnik Klettwelding entwickelt werden. Technologische Highlights, wie z. B. die direkte Montage von Leistungstransistoren auf einen 3D-gedruckten Flüssigkeitskühlkörper, sollen zur erheblichen Miniaturisierung und Leistungssteigerung beitragen. Die erforderlichen Zuverlässigkeitsuntersuchungen werden vom Projektpartner am AVT-Institut der TU Dresden durchgeführt.

Digitaler Rundgang

Beim digitalen Netzwerktreffen unternahmen die Teilnehmer einen virtuellen Rundgang durch die Lern- und Forschungsfabrik des Lehrstuhls für Produktionssysteme (LPS) an der Ruhr Uni Bochum. Diese Einrichtung bildet ein produzierendes KMU mit verschiedenen digitalisierten mechanischen Bearbeitungsmaschinen und einer digitalisierten Handmontagelinie ab. Die Schwerpunkte des LPS liegen auf Teilautomatisierungen und Mensch-Roboter-Kollaborationen. Damit ist der Lehrstuhl ein wichtiger Partner im Konsortium, weil auch in der Fertigung und Montage von 3D-Elektronik neuartige Fertigungs- und Montageprozesse benötigt werden. Im Kontext von Industrie 4.0 werden am LPS neue digitale Fertigungs- und Montageprozesse entwickelt.

Den Impulsvortrag hielt Dr. Bob Wittig, Abteilung Werkstoffentwicklung Metall & Korrosionsschutz UA Elektrik/Elektronik bei Volkswagen. Der Experte skizzierte mögliche Anwendungsfelder der 3D-Elektronik in Kraftfahrzeugen mit charakteristisch sehr hohen Anforderungen an die Langzeitzuverlässigkeit. Entsprechend umfangreich und langwierig sind die Tests, bevor eine neue Technologie akzeptiert und etabliert wird. Künftige Anwendungsgebiete für höher integrierte Komponenten und funktionale Integration sind im Innen- und Außenraum von Fahrzeugen, die in der Runde diskutiert wurden.

Netzwerk öffnet sich für neue Mitglieder

Das Netzwerk 3D-Elektronik soll auch künftig weiter unter der Leitung der Technologieberatung Jöckel Innovation Consulting geführt werden. Aktuell beteiligen sich 15 Unternehmen und Forschungseinrichtungen mit unterschiedlichen Kompetenzbereichen am Netzwerk: Embedded-Leiterplatte, Flexsubstrate, Kunststoff, Keramik, AVT und Mikrosystemtechnik. Im Netzwerk können auf kurzem Weg Informationen ausgetauscht und Partner für gemeinsame Forschungsprojekte zusammenfinden. Zur Fortführung des Netzwerkes ist jährlich ein Innovationstag geplant. Die Mitglieder erhalten im Netzwerk verschiedene Services wie Tech-Talks, Entwicklung gemeinsamer Demonstratoren, Informationen zu Förderprojekten, Beratung für Fördermittel sowie die weitere Pflege der Webseite www.3D-Elektronik.net. Interessierte Unternehmen wenden sich bitte an Ann-Cathrin Hubschneider (E-Mail: a.hubschneider@joein.de) von Jöckel Innovation Consulting und an Hanno Platz (E-Mail: h.platz@ged.pcb-mcm.de) von GED mbH, Leiter des FED-Arbeitskreises 3D-Elektronik, der technische Fragen beantwortet.

Formula Student an der H-BRS: 2021 weiter auf der Erfolgsspur

Auch in diesem Jahr konnten die E-Motorsportler der Hochschule Bonn-Rhein-Sieg (BRS Motorsport e.V.) große Erfolge bei den Formula Student Events feiern. So erzielte das Studierendenteam mit seinem Elektro-Rennwagen G21e, Spitzname „Luna“, sogar erstmals einen Gesamtsieg.

GED sponsert seit vielen Jahren den Elektromotorsport an der Hochschule Bonn-Rhein-Sieg. Aktuell arbeiten zwei Mitglieder des BRS-Motorsportteams bei GED.

Höhepunkt der Saison war für BRS die Formula Student Spain auf der Rennstrecke Barcelona-Catalunya. Hier belegte das Team aus Sankt Augustin in vielen Einzeldisziplinen wie im Beschleunigungs- und im Langstreckenrennen Top-Platzierungen. Den 75-Meter-Sprint schaffte Luna in herausragenden 3,48 Sekunden. In der Disziplin Cost und Manufacturing Event (Kostenanalyse) erreichte das Team 95 von 100 Punkten, im Engineering Design Report (Konstruktionsbericht) sogar die Höchstpunktzahl. Spannung bis zuletzt: Erst bei der Siegerehrung realisierte das Team, dass es den ersten Platz bei der Formula Student Spain 2021 errungen hatte. Dies war der erste Gesamtsieg für den BRS Motorsport bei einem Weltranglisten-Event.

Wie in Spanien konnte die BRS-Crew auch bei der Formula Student Germany (FSG) im September auf dem Hockenheimring den Sieg beim Cost Event für sich verbuchen. Das war für das Team der erste Sieg in einer Teildisziplin bei der FSG. Insgesamt reichte es in einem starken Teilnehmerfeld den achten Platz. Beim letzten Event der Saison 2021, der Formula Student Alpe Adria in Kroatien, holt Luna den dritten Platz in der Disziplin Beschleunigung.

Das Team freut sich über die Ergebnisse der Wettbewerbe. Bereits seit Saisonende tüftelt es am Elektroflitzer für die Renn-Events im Jahr 2022.

GED gratuliert zu den großen Erfolgen und den gezeigten Leistungen in einem hochkarätigen, internationalen Wettbewerbsumfeld!

Weitere Informationen zum E-Motorsport an der Hochschule Bonn-Rhein-Sieg finden Sie hier.