Beschaffungsprobleme vermeiden: Obsolescence Managment by Design

Welche Maßnahmen können in der Design- und Entwicklungsphase helfen, um die zunehmenden Schwierigkeiten bei der Beschaffung elektronischer Bauteile zu reduzieren?

Auf dem ersten Quartalsmeeting des COG Deutschland e.V. am 12. März 2019 in Kassel hat GED-Geschäftsführer Hanno Platz zu dieser Frage einen Vortrag gehalten. Der Industrieverband Component Obsolescence Group Deutschland e. V. (COGD e.V.) bietet Gleichgesinnten eine Plattform zum Thema Obsolescence Management. Ziel ist es, die Folgen der Nichtverfügbarkeit von Komponenten in Produkten zu minimieren oder diesen Fall zu verhindern.

In der Elektronikbranche verschärft sich aktuell die Problematik von längeren Lieferzeiten, von knappen Verfügbarkeiten oder auch der kurzfristigen Abkündigung von Bauteilen. Dabei gibt eine ganze Reihe von neuen Technologien, die das Thema Bauteile-Obsoleszenz in den nächsten Jahren noch deutlich verschärfen. Neue Megatrends in der Elektronik benötigen erheblich mehr Bauteile durch höhere Stückzahlen, steigende Funktionalität und kürzere Lebenszyklen. Dies sind Trends wie:

- Autonomes Fahren

- E-Mobilität

- Neue Energien, Smart Home

- Robotik, Drohnen

- Internet of Things (IoT), Industrie 4.0

- Big Data, Künstliche Intelligenz

- Smart-Watch, Smart-Speaker, VR-Brillen

- Wearables

- Smartphones

- 5G-Mobilfunk.

Stichwort höhere Stückzahlen: Allein bei der Sprachbox Alexa wird in diesem Jahr eine Steigerung der Produktion von 100 auf 250 Millionen Stück erwartet. Auch die Elektromobilität startet jetzt mit 5,6 Millionen E-Fahrzeugen (= 64 % plus, 50 % davon China) spürbar durch, wobei die komplette Infrastruktur wie Ladestationen zu einer großen Zusatznachfrage führt. Der Bedarf an diskreten Bauteilen in den E-Autos ist erheblich. So sind im Schnitt in jedem dieser Fahrzeuge rund 3.000 MLLC-Kondensatoren verbaut, im Tesla sind es sogar 18.000 Kondensatoren pro Wagen. Auch die Mengen an diskreten Bauteilen in Handys steigen enorm. Im aktuellen iPhone 10 wurden 30-40 % mehr Bauteile eingesetzt. So sind sage und schreibe in jedem Handy etwa 1.000 MLLc und 1.200 Widerstände verbaut.

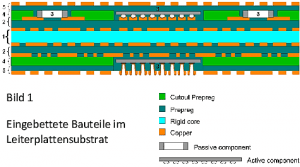

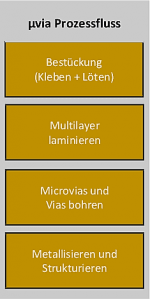

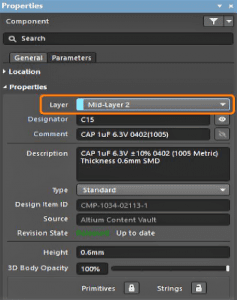

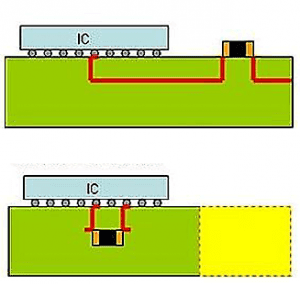

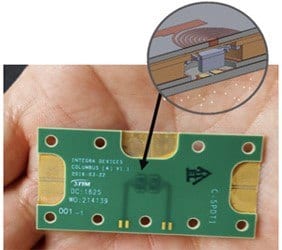

Kleine statt große Bauformen

Für Deutschland und Europa ergibt sich daraus jedoch noch eine weitere Problematik. Rund 90 % des weltweiten Bedarfs an elektronischen Bauteilen wird in Asien verarbeitet! Auf Europa entfallen nur 7-8 %. Es liegt also auf der Hand, wer den größeren Einfluss auf Verfügbarkeit und Lieferzeiten von Bauteilen hat. Das führte bereits 2018 zu Engpässen, selbst bei Widerständen und Kondensatoren. Die großen Supplier von Rs und Cs gehen vermehrt dazu über, größere Bauformen komplett aus dem Programm zu nehmen. So sind Bauteile mit Bauform 1206 und 0805 bei Murata Co. abgekündigt, selbst die Bauform 0603 wird nur in geringeren Mengen produziert. Durch den enormen Bauteilebedarf bei den Smartphones sind dort inzwischen Bauform 0201 und 01005 das, was strategisch in größter Stückzahl produziert wird. Übrigens werden auch für Standard-Industrieanwendungen die kleinen Bauformen immer unumgänglicher. Gerade bei hochpoligen FPGAs oder Microcontrollern sind viele Abblockkondensatoren möglichst nahe am jeweiligen Bauteilepin zu platzieren. Das gelingt dann nur mit Bauform 0201 oder besser noch kleiner.

Beschaffung mit Weitsicht

Das bedeutet, in der Entwicklungs- und Designphase ist es zukünftig wichtiger denn je, besondere Vorkehrungen im Hinblick auf Obsoleszenz und lange Lieferzeiten zu treffen. Natürlich wäre die erste Forderung stets, eine Second Source zu bestimmen. Das ist leider nicht immer möglich. Dagegen sind generelle Festlegungen, wie nur ein Fabrikat für Keramikkondensatoren festzuschreiben, sehr eingrenzend und gefährlich. Der Einsatz von speziellen Modulen, z. B. Powermodule, ist in der Regel auch damit verbunden, dass nur Bauteile von einem Hersteller verwendet werden können.

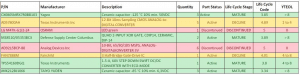

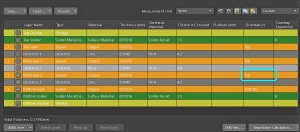

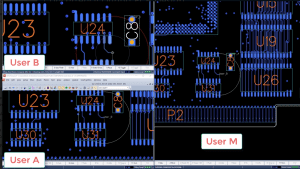

Aber womit fängt die Lösung des Problems dann an? Bei der Bauteile-Auswahl steht der Entwickler vor einer großen Anzahl an Optionen. Ein Beispiel: Bei einem MLLC mit 100 nF und Bauform 0402 bietet ein bekannter Distributor derzeit schon einmal 374 Möglichkeiten an. Lässt man hier dem Entwickler in der Entscheidung freie Hand, entstehen schnell unnötige Einschränkungen. Deshalb empfiehlt sich bei der Beschaffung und Festlegung neuer Bauteile eine klare strategische Vorgabe oder eine Prüfung durch entsprechende Abstimmung und Zusammenarbeit mit der Einkaufsabteilung. Bei der ausgelagerten Fertigung über EMS-Dienstleister ist es wichtig, deren Lager zu berücksichtigen und/oder zu kennzeichnen, welche Bauteile nicht auf einen Typen oder Hersteller festgelegt sind. Ausgewählte Bauteile sollten eindeutig identifizierbar sein. Neben der Festlegung des elektrischen Werts und der Bauform des Bauteils sind auch Angaben über die Spannungs- und Toleranzklasse relevant.

Welche Vorgehensweise ist sinnvoll und welche Angaben sollte die Stückliste/BOM enthalten?

A. Gezielte Auswahl neuer Bauteile:

- Analyse zur Produktdefinition in der Vorprüfung (PDR), Critical Design Review (CDR) etc.

- Klassifizierung der eindeutigen, zweideutigen und fehlerhaften Teileidentifikationen/-beschreibungen

- Identifizierung der Ursachen für unzureichende Bauteilebeschreibungen

- Alternative Bauteile, Second Source

B. Minimal Angaben für eine exakte Bauteile-Identifikation:

- Name und/oder Beschreibung

- Teilenummer(n) aus dem OEM(s)/OCM(s)

- Namen der OEM(s)/OCM(s)

- Hersteller-Code (CAGE = Commercial-and-Government-Entity-Code)

- NSN-/NATO-Nummer (National Stock Number oder NATO Stock Number)

- Anzahl der benötigten Teile pro Baugruppe

C. Darüber hinaus sollte man folgende Punkte generell berücksichtigen:

- Verfügbarkeit der ausgewählten Bauteile prüfen, insbesondere bei neuen Typen

- Abkündigungen und „End of Life“ (EOL) und „Part Change Notification“ (PCN) prüfen

- Immer A-Bauteile wie Controller, Speicher, Stecker, Display usw. auf Lieferzeiten prüfen

- Auch C-Bauteile frühzeitig auf Lieferfähigkeit prüfen

- Frühe Abstimmung mit dem Baugruppenfertiger, BOM-Analyse

- Materialbeschaffung für Serienstart früher planen und Material früher bestellen

- Regelmäßige Überwachung der Materialien

Kurz gesagt, es empfiehlt sich, weitsichtig zu denken und zu planen:

- Ersatztypen festlegen, Second Source in die BOM aufnehmen.

- Bei kritischen Bauteilen alternative Gehäuseformen im Layout vorsehen.

- Frühzeitige Serienplanung und Materialbeschaffung, ggf. Lagermenge anlegen.

- Vorsicht bei Bauteilen wie Displays, MEMS Mikro, Powermodule usw., Material optional selbst bevorraten.

- Ggf. „alternative shapes“ für kritische Bauteile vorsehen.

- Je größer die Serie, desto wichtiger ist eine frühzeitige Planung.

- Bei Ersatzbeschaffung über Broker oder Refurbished-Anbietern ist Vorsicht geboten.

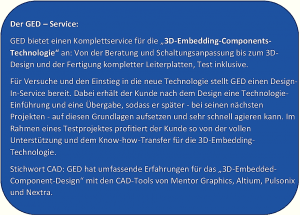

GED verfügt aus mehr als 30 Jahren Erfahrung in Entwicklung und Design über Designstrategien, die bestimmte Risiken deutlich minimieren können. Beispiele werden in einer der nächsten Ausgaben des Newsletters gezeigt.

Möchten Sie mehr über Obsolescence Managment by Design erfahren?

Rufen Sie uns an:

+ 49 (0) 2247 92 19-0.

Oder senden Sie uns Ihre Nachricht.