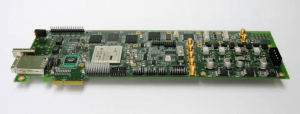

Ob es um Leiterplatten für moderne Telekommunikation, autonome Fahrzeuge, Optronikanwendungen oder Embedded Boards usw. geht, sie alle weisen aktuell eine weiter steigende hohe Komplexität auf. Anschlusszahlen von 15.000 bis 20.000 ja sogar bis 30.000 Verbindungen sind heute keine Seltenheit mehr. Die Folge: Bei einem professionellen, soliden Leiterplattendesign kommen da schnell mehrere Monate nur für das PCB-Design zusammen. Um diese Dauer zu verkürzen, setzt GED seit einiger Zeit auf die High-End-CAD-Toolchain Xpedition® Enterprise von Mentor Graphics. Der Erfolg ist messbar und eröffnet eine neue Dimension: Durch die Multiuserfunktionen des Tools kann GED die Designzeit auf 50-60 Prozent reduzieren.

Concurrent Engineering

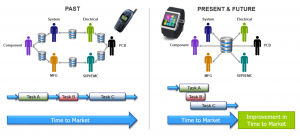

Time to market (TTM) ist in allen innovativen Branchen der entscheidende Erfolgsfaktor: Heute sind es bereits zwei oder drei Monate mehr oder weniger Zeit, die darüber entscheiden, wer im Wettbewerb die Nase vorn hat. Entsprechend wichtig sind möglichst kurze Designzeiten auch bei hochkomplexen Leiterplatten.

Ein Beispiel: Bei hochintegrierten Bauteilen wie FPGAs mit 2.500 Anschlüssen sowie Speicherbänken, mehreren DDR-Speichern, Peripherie und Steckern addiert sich die Zahl der Anschlüsse sehr schnell. Hinzu kommt natürlich, dass die erforderlichen Verbindungstopologien für Highspeed-Signale impedanzdefiniert und differentiell als Paare mit Längenausgleich geführt werden müssen. Dafür wird herkömmlich eine Designzeit von acht bis zwölf Wochen benötigt, wenn alle Parameter feststehen. Mit der „Concurrent-Engineering-Methode“, bei der mehrere Designer gleichzeitig an einem Design arbeiten, hat GED jetzt in verschiedenen Designprojekten nachgewiesen, dass sich dieses Zeit real auf vier bis sechs Wochen reduzieren lässt.

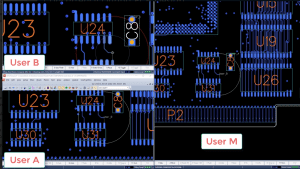

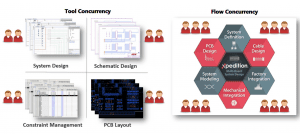

Basis des gleichzeitigen Arbeitens mehrerer Designer an einem Design ist bei GED das High-End CAD-Toolpaket von Mentor Graphics, Xpedition. Es organisiert diese Zusammenarbeit sicher und zuverlässig. Dafür sorgen Multi-User-, Multi-Site-Tool- und Flow-Based-Concurrent-Engineering während des gesamten Produktentwicklungsprozesses. Alle Teammitglieder können mit der kompletten Datenbank in Echtzeit arbeiten, ohne dass sie neu partitioniert und neu zusammengestellt werden muss. Auch die Schaltplan- und Constraining-Tools verwalten die Änderungen aller Benutzer und senden kontinuierlich Updates an das gesamte Team.

Alle User sehen, in welchen Bereichen die anderen arbeiten. Dabei lassen sich die Bereiche für den einzelnen definieren und eingrenzen. So kann etwa nur der Spezialist für Schaltregler den Powerbereich routen und der Speicherbereich wird von einem anderen Experten geroutet. Bereits bei der Schaltplanerstellung und dem Constraining mit dem CES-Tool ist eine parallele Zusammenarbeit möglich.

Zusammenfassend gesagt, GED kann im gesamten Designflow, vom Schaltplanentwurf über das Constraining bis zum Design, mit gleichzeitig arbeitenden Teams auch eine sehr komplexe Leiterplatte in nur wenigen Wochen bzw. Monaten entwerfen: Concurrent Engineering reduziert nachweislich die Konstruktionszykluszeit um 40 bis 70 Prozent selbst für die komplexesten Leiterplatten. GED hat dazu eine Methode entwickelt, mit der das Unternehmen an den entscheiden Stellen der Designphase durch den gezielten Einsatz eines eingespielten Spezialistenteams in deutlich kürzerer Zeit hervorragende Ergebnisse erzielt.

Concurrent Engineering auf einen Blick – die Kundenvorteile der parallelen Entwicklung in Echtzeit:

- Verbessertes time to market durch Beschleunigung des Produktentwicklungsprozesses. Ermöglicht durch die Fähigkeit aller Teammitglieder, gleichzeitig an allen Designobjekten zu arbeiten.

- Reduzierte Kosten für die Produktentwicklung durch optimierte Ressourcenauslastung und Verbesserung der Gesamtproduktivität.

- Verbesserte Designqualität: Der Concurrent-Engineering-Prozess eröffnet Zeitfenster für Aufgaben, die sonst oft nicht in die Terminplanung passen; zum Beispiel laufende Power-Integrity-Simulationen oder Fertigungs-Bewertungen zeitgleich mit dem PCB-Layout.

- Besonders wichtig: Starke Differenzierung im Wettbewerb durch schnellere Marktreife und höhere Qualität. Dieser Vorteil ist sowohl für das aktuelle Produkt als auch für alle nachfolgenden Produkte realisierbar.

Mehr über Concurrent Engineering und 3D-Elektronik erfahren Sie hier.

Wollen Sie mehr darüber erfahren, wie GED mit Concurrent Engineering kurze Designzeiten auch bei komplexen Leiterplatten erreicht? Sprechen Sie mit uns über Ihre Anforderungen!

Rufen Sie uns einfach an:

+ 49 (0) 2247 92 19-0.

Oder senden Sie uns Ihre Nachricht.