Design Challenge 2020 – Moore’s Law in der dritten Dimension

Technologie- und Markttrends sowie Regulierungen werden auch in den nächsten Jahren gravierende Anforderungen an die Systemintegration in der Elektronik stellen. So erwarten Experten, dass in den kommenden vier Jahren rund 2 Milliarden IoT-Sensoren benötigt werden, um die Ideen aus der 4. Industrierevolution für die neuen cyberphysischen Fertigungsgenerationen in „Industrie 4.0“ umzusetzen. Aber auch andere Trends und gesetzliche Regelungen, wie das Ziel der CO2-Reduktion um 40 Prozent, erfordern zum Teil drastische Anstrengungen zu forcierten Weiterentwicklungen. Diese basieren fast immer auf einer intelligenten Kombination von Elektronik und Software. Anders gesagt: Moore‘s Law besteht auch weiterhin. Es ist um mehrere Dimensionen auszubauen, wenn die zunehmende Leistungsfähigkeit der Integration von Bauteilen, Leiterplatten und Verbindungselementen den Miniaturisierungsanforderungen folgen sollen.

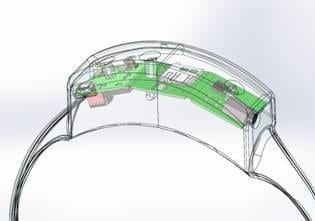

Aktuell führen eine Vielzahl von Marktentwicklungen, Trends oder gesetzlichen Änderungen zu hohem Entwicklungsbedarf in der Elektronik. Die Anforderungen an höhere Leistungs- und Funktionsdichte, Miniaturisierung und Integration steigen erheblich an. Zunehmend werden dreidimensionale Integrationen und mechatronische Lösungen eingesetzt und die Entwicklungen werden interdisziplinär. Einfaches Beispiel: Eine moderne Lichtschranke ist heute ein hochintegriertes System in der Größe eines Würfelzuckers. Optische Sensorsignale werden mit hochintegrierter Analogtechnik aufbereitet und per µController weiter verarbeitet. Integriert werden die Elektronik und Optronik in einem Kunststoffgehäuse mit integriertem Stecker, wobei die Wärmeableitung des ASICs über das Gehäuse erfolgt. Aufgrund des begrenzten Bauraums müssen HDI-Leiterplatten mit µVias verwendet werden. Gesteuert durch umfangreiche Software bildet das Ganze dann ein hochintegriertes mechatronisches System.

Ein anderer Faktor, der zunehmend entscheidend wird, sind die Entwicklungszeiten. Zwar sind etwa in der Automobilindustrie mit Großserien-Stückzahlen drei bis vier Jahre vom Konzept bis zum Serienstart üblich, in manch anderen Branchen stehen aber nur sechs Monate zur Verfügung. Doch auch diese Zeiten werden künftig durch neue Methoden und paralleles Arbeiten von Entwicklerteams reduziert (Concurrent Engineering). Der Einsatz von modernen Konstruktions- und Simulationstools hilft, Redesigns und Entwicklungszeiten zu reduzieren.

Höhere Verbindungsdichte durch Bauteile-Miniaturisierung und steigende Anschlussanzahlen

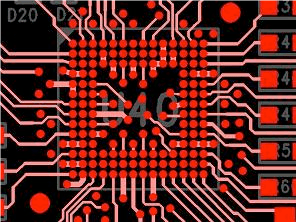

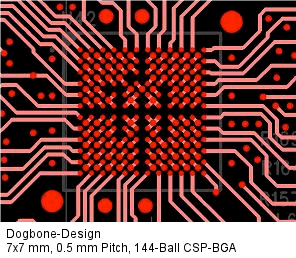

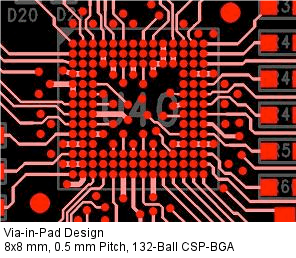

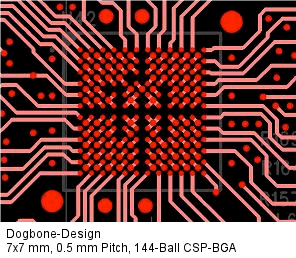

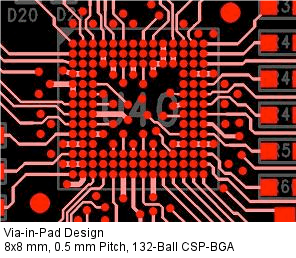

Neue Bauteilegehäuse werden zunehmend kleiner und haben höhere Anschlusszahlen. LQFP, QFN oder MLP Gehäusebauformen haben bis ca. 100 Anschlüsse bei einer Kantenlänge um die 5 mm. µBGA oder CSP Bauteile reichen bis weit über 1.000 Anschlüsse. Diskrete Bauteile gibt es in winzigen Gehäusebauformen wie 0201, Micro-MELF oder SOT-883 mit 3 Anschlüssen und mit einer Größe von nur 1 x 0,6 x 0,5 mm. Damit lassen sich inzwischen Miniaturisierungsgrade erzielen, die ehemals nur mit COB-Technik, also mit ungehäusten Bauteilen, erzielt wurden. Es gibt heute moderne FPGAS wie Kintex 7™ von XILINX, die bis zu 1.156 Anschlüsse (I/O´s) haben oder auch ASIC Bauteile mit über 2.500 Anschlüssen, mit Pitchmaßen bis runter auf 0,4 mm.

So genannte HDI-(High-Density-Interconnection) Leiterplattentechnologien, die eine höhere Verbindungsdichte durch Einsatz von Microvias (150 µm) und Burried Vias in Verbindung mit feinen Leiterstrukturen unter 150 µm haben, können die Verbindungsdichte einer Leiterplatte signifikant steigern und ermöglichen den Anschluss von Bauteilen mit hoher Pin-Dichte. Je nach Größe und Anforderung werden heute auch Leiterstrukturen von 50 µm in Serie produziert. Künftig wird für Pitchmaße von nur 0,3 mm eine Leiterbreite von, zumindest partiell, nur 30 µm benötigt.

Steigende Signalübertragungsraten im Multi-Gigabit Bereich

Neue FPGA-Generationen wie der Xilinx Virtex 7 haben neben weiteren DSP-Ressourcen mit dem DDR3-Speicher-Contoller die Übertragungsgeschwindigkeit von 800 Mbit/s auf 1600 Mbit/s gesteigert. Außerdem hat sich die Bandbreite des integrierten PCI-Express-Controllers auf 8 Gbit/s erhöht, sodass eine noch schnellere Datenübertragung vom FPGA zum Host möglich ist.

Bei der weit verbreiteten Schnittstelle „Universal Serial Bus“ konnten mit dem USB 3.0 bereits Signalraten von 5 Gbit/s erreicht werden, jetzt ist mit USB 3.1 ein Transfer mit bis zu 10 Gbit/s möglich. Selbst für USB 3.0 wird für die 5 Gbit/s eine entsprechende Leitertopolgie benötigt, damit die Übertragung störungsfrei funktioniert.

Der Videostandard „Ultra High Definition Video“ UHD-1 (4k) benötigt mehr als 10,2 Gbit/s, weshalb HDMI in der Version 2.0 bis zu 18 Gbit/s liefern kann. Hauptänderung ist die Anhebung der maximalen Bandbreite auf 18 Gbit/s, wodurch Ultra-HD-Inhalte mit 60 Bildern pro Sekunde wiedergegeben werden können. Allerdings wurde übergangsweise auch eine kleinere Datenrate mit der niedrigen Farbquantisierung 8 Bit und 4:2:0 erlaubt, um vorhandene HDMI-1.4-Chips nutzen zu können. Eine weitere Hürde stellt die neue Kopierschutz-Norm HDCP-2.2 dar, die in vollwertigen HDMI-2.0-Anschlüssen vorgeschrieben ist.

Um diese hochfrequenten Signalgeschwindigkeiten störungsfrei zu erzielen sind entsprechende Topologien und ein angepasste Leiterbahnrouting-Methode erforderlich. Für die LVDS-Signalübertragung ist eine differentielle Signalführung mit gleicher Leitungslänge für Hin- und Rückleiter erforderlich. Die Signale benötigen einen Lagenaufbau mit angepasstem Wellenwiderstand (Impedanz).

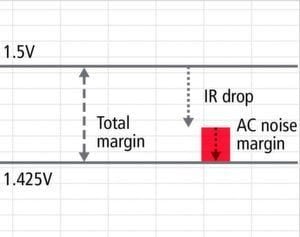

Man könnte die Aufzählung noch lange mit weiteren Beispielen fortführen. Natürlich bringen die neuen Bauteile und Schnittstellen auch ein komplexeres Powering mit sich. Oft werden 5 – 8 verschiedene Spannungen benötigt, die i. d. R. mit hochgetakteten Linearreglern erzeugt werden. Diese müssen nach festen Regeln designt werden und sind in einem Lagenaufbau für das Powerkonzept entsprechend einzuplanen.

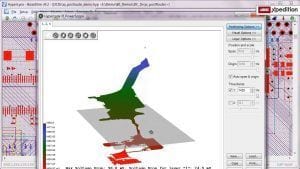

Bei komplexen Multilayern wird es zunehmend erforderlich, die Homogenität der Versorgungsflächen, die wichtig für die zuverlässige Signalübertragung und die EMV-Festigkeit sind, mittels „Power Integrity Simulation“ zu überprüfen.

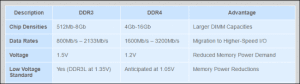

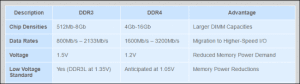

Speicherdichten erhöhen sich zunehmend, DDR4

Die DDR-SDRAM-Technologie hat ihre vierte Generation erreicht. Die DDR4-SDRAM-Schnittstelle erreicht eine maximale Datenrate von 3,2 Gbit/s (d.h. eine Taktrate von 1,6 GHz). Beim Design gibt es vier wichtige Anforderungen für die Platzierung und das Routing von DDR4-SDRAM-Schnittstellen mit Multi-Gigabit-Übertragung. Diese großen Herausforderungen umfassen die Routingtopologie und das Terminierungssystem für die Netze mit mehreren Speichern, das eine Routing-Technik mit geringem Übersprechen erfordert. Es werden spezielle Designmethoden eingesetzt, um die Impedanzsprünge aufgrund von Durchkontaktierungen zu minimieren.

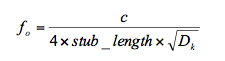

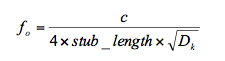

Die Routing-Technik für mehrere Speicherbausteine erzeugt mit der herkömmlichen Art von Routing mit Baumtopologie sogenannte „Trace Stubs“, die die Signalintegrität des Übertragungskanals verschlechtern. Die Wirkung von Stubs ist unten in der Formel erläutert, nach der die Resonanzfrequenz oder die Bandbreite der Übertragungsleitung umgekehrt proportional ist zur Stublänge. In der herkömmlichen Baumtopologie führt der „Trace Stub“ mit der Zunahme der Anzahl von Speichern zu unerwünschten Verlängerungen, die Störungen hervorrufen.

fo = Resonanzfrequenz (Hz), c = Lichtgeschwindigkeit (1.18 x 10 10 Zoll/s), stub_length in inches, Dk = Dielektrizitätskonstante

Der Einsatz von verlustarmen Materialien, sogenannte „High speed laminate“ wie Megtron (Panasonic) oder I-Tera (Isola) wird ebenso erforderlich wie ein „backdrilling“ von durchgehenden Vias. Für das Routing der Leiterbahnen ist ein Tuning der Leitungslängen erforderlich und das mit sehr engen Toleranzen. Ohne diese Designmaßnahmen ist eine zuverlässige Signalübertragung nicht mehr möglich.

Zur Steigerung der Zuverlässigkeit und auch zum Qualitätsnachweis der Gigbit-Übertragungssysteme setzt GED das SI-Simulationswerkzeug Hyperlynx von Mentor Graphics ein. Damit lässt sich die Signalintegrität in Form der Augendiagramme simulieren. Mittels „Presimulation“ kann bereits bei der Planung der Topologie des Multilayers eine Prüfung der berechneten Impedanzwerte vorgenommen werden.

Hochstromanwendungen und Entwärmung

Hochleistungsprozessoren, High-Power-LEDs und MOSFETs haben eins gemeinsam: Sie erzeugen hohe Verlustleistung, also Wärme. Diese muss abgeleitet werden, weil sie die Funktion und die Lebensdauer negativ beeinflussen, bzw. bis zur Zerstörung führen. Moderne SMD-Leistungsbauteile bieten die Möglichkeit, die Wärme über die Leiterplatte abzuleiten. Verschiedene Designmaßnahmen sind möglich. Mittels Thermosimulation lässt sich bereits in der Entwicklungsphase das Zusammenwirken von mehreren Bauteilen auf der Leiterplatte im Voraus feststellen. Der Einbau von partiellen Coolingcoins kann den Einsatz teurer Kühlkörper ersetzen.

Die heutigen und kommenden Anforderungen sind vielfältig: Im Bereich der Hochstromtechnik, ggf. auch in Kombination mit Hochspannung von über 500 Volt, müssen Ströme von über 100 Ampere auf der Leiterplatte geführt werden. Die Bereiche Automotive und Elektromobilität benötigen zunehmend die Kombination von Signal- und Leistungselektronik für moderne Geräte. Dies gilt jedoch auch in anderen Bereichen wie Motorsteuerung und Energieverteilung. Hinzu kommen auch hier hohe Anforderungen zur Entwärmung der Bauteile, an die Anschlusstechnik für die hohen Leistungen und an das Housing. Die hochintegrierten leistungselektronischen Geräte müssen so konstruiert werden, dass sie die entsprechende Zuverlässigkeit vorweisen.

Darüber hinaus gibt es noch viele weitere Anforderungen an die Systemintegration, die es in den nächsten 4 bis 5 Jahren umzusetzen gilt. Themen wie zunehmend komplexere Powering- oder Testkonzepte, Hochfrequenz für Radar, Mechatronik und funktionale Integration und insbesondere „kostenoptimiertes Design“ – das sind die Herausforderung für 2020.

Nicht mehr viel Zeit bis dahin!

GED unterstützt Sie mit 30 Jahren Erfahrung und Spezialkenntnissen, setzt modernste CAD- und Simulationstools ein und verfügt über ein erfahrenes Team von Spezialisten für die verschiedenen Aufgabenbereiche, auch bei komplexen Projekten.[

Wollen Sie mehr über Lösungen für die „Industrie 4.0“, Simultaneous Engeneering, Miniaturisierung und die Integration von Elektronik und Mechanik erfahren?

Rufen Sie uns an –

+ 49 (0) 2247 92 19-0.

Oder senden Sie eine Nachricht.