Altium Designer Release 15: Neue starke Funktionen für die gestiegenen Highspeed-Anforderungen – auch im 10-GHz-Bereich

Altium hat über die letzten Jahre die Funktionalität des Altium Designers so massiv ausgebaut, dass bei GED neben dem „Mentor Graphics Design flow“ die zweite CAD-Schiene mit Altium Designer deutlich erweitert wurde. Jetzt hat Altium im Highspeed-Bereich mit wichtigen Features nachgezogen.

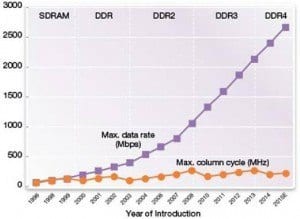

Hatten DDR2-Speicher im Jahr 2010 auf dem I/O-Bus noch Taktraten von 1 Gbit/sek, so steigen aktuell bei den DDR4-RAMs die maximalen Dataraten sogar bis 7 Gbit/sek. Damit die Speicher störungsfrei arbeiten sind entsprechende Techniken erforderlich – und auch Designtechniken auf der Leiterplatte. Das Bild zeigt die stark angestiegenen Datenraten der letzten Jahre im Speicherbereich.

Hatten DDR2-Speicher im Jahr 2010 auf dem I/O-Bus noch Taktraten von 1 Gbit/sek, so steigen aktuell bei den DDR4-RAMs die maximalen Dataraten sogar bis 7 Gbit/sek. Damit die Speicher störungsfrei arbeiten sind entsprechende Techniken erforderlich – und auch Designtechniken auf der Leiterplatte. Das Bild zeigt die stark angestiegenen Datenraten der letzten Jahre im Speicherbereich.

XSIGNALS: Verbindungsdesign für Speicher

Unter dem Begriff „XSIGNALS“ bietet der Altium Designer jetzt Funktionen für das Routing von „T-Junctions“ oder „fly-by-net Topologien“, wie sie für das Routing von dynamischen Speichern, wie z. B. DDR2- oder DDR3-RAMs, benötigt werden. Wenn mehrere Speicherbausteine zu verbinden sind, wird es immer aufwendiger, die nach JEDEC vorgegebenen Verbindungstopologien auf der Leiterplatte umzusetzen. Altium bietet jetzt mit XSIGNALS die Möglichkeit, Leitungen in Netzgruppen zusammenzufassen und sie dann in Netzklassen mit Vorgabewerten zu belegen wie der maximalen Länge zwischen den Pins.

Neue Speichergenerationen stellen neue Anforderungen an das Highspeed-Design

Neue Generationen von Speichern wie DDR4 stellen wiederum erweiterte Anforderungen an das Highspeed-Design. Das Längenmatching der Leiterbahnen erfordert noch kleinere Toleranzen, damit die Schaltungen sicher funktionieren. Beim Einsatz eines Xilinx KINTEX 7-FPGA mit DDR3-Speichern beispielsweise beträgt der maximale Delay zwischen den Adress- und Controlsignalen und dem differentiellen Clockleitungspaar 25 Picosekunden. Der maximale Delay zwischen den DQ-Leitungen und den differentiell geführten DQ/DQS# innerhalb einer Lane darf 5 Picosekunden nicht überschreiten. Das bedeutet: Der maximale Längenunterschied innerhalb einer Bytelane mit den Signalen DQ, DM und DQS muss weniger als 1 mm betragen.

Constraining mit Komfort

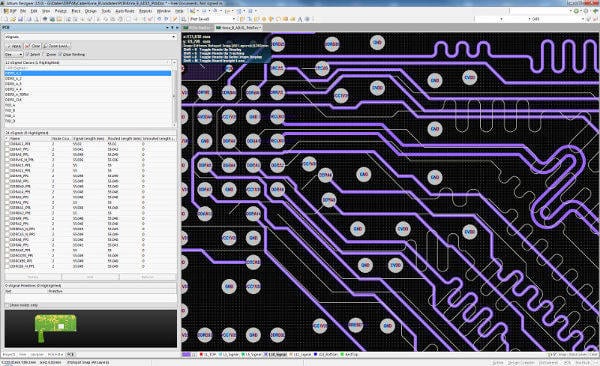

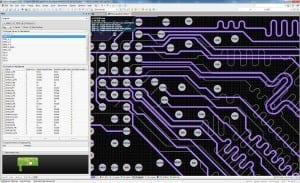

Mit der ALTIUM Version 15 stehen komfortable Funktionen für die Festlegung der Verbindungsregeln (Constraining) zur Verfügung. Das Bild zeigt einen Ausschnitt der Leiterführung zwischen µController und den Speichern. Gut zu erkennen ist der typische „meanderförmige Längenausgleich“ der Leiterbahnen auf zwei eingeblendeten Lagen. Der Längenausgleich ist erforderlich, um unterschiedliche Signallaufzeiten auszugleichen.

Mit der ALTIUM Version 15 stehen komfortable Funktionen für die Festlegung der Verbindungsregeln (Constraining) zur Verfügung. Das Bild zeigt einen Ausschnitt der Leiterführung zwischen µController und den Speichern. Gut zu erkennen ist der typische „meanderförmige Längenausgleich“ der Leiterbahnen auf zwei eingeblendeten Lagen. Der Längenausgleich ist erforderlich, um unterschiedliche Signallaufzeiten auszugleichen.

Durchkontaktierungen zählen zur Leiterlänge

Bei den Toleranzen der maximalen Leitungslängen und dem Längenmatching von maximal 1 mm spielt auch die Leiterlänge über die Durchkontaktierungen eine Rolle: Ein Lagenwechsel von der Top- zur Bottomseite ergibt bei einer Leiterplatte mit einer Standarddicke von 1,5 mm bereits einen Längenwert, der über der erlaubten Toleranz liegt! Dieses Manko wurde von Altium erkannt, die Durchkontaktierung wird jetzt präzise berechnet: Dabei wird die tatsächliche Länge der Leitung über die Vias, auch über Blinde- oder Sacklöcher der Innenlagen, berücksichtigt.

Das Bild zeigt den berechneten Weg über die Sacklöcher und einen Teil der durchgehenden Bohrungen mit der roten Linie in 3D-Darstellung.

Das Bild zeigt den berechneten Weg über die Sacklöcher und einen Teil der durchgehenden Bohrungen mit der roten Linie in 3D-Darstellung.

Erst Constraining, dann Routing

Das Signal-Constraining, also die Eingabe der Verbindungsregeln, muss vor dem Routing vorgenommen werden. Dazu sind die Bauteile-Datenblätter auf die elektrischen Parameter hin zu betrachten und die Vorgaben für die Anordnung und Verlegung der Leiterbahnen entsprechend zu planen. Bereits zu diesem frühen Zeitpunkt ist zu prüfen, welche Leiterplattentechnologie überhaupt eingesetzt werden kann: Ansonsten lassen sich die Vorgaben im Layout gar nicht umsetzten. Im ungünstigsten Fall lässt sich das Layout nicht routen. Die Einstellungen erfolgen im „Rules Editor“.

Power-Konzept: Planung der Versorgungssysteme

Ein weiterer wichtiger Aspekt ist die Planung des Versorgungssystems. Speicher, Microcontroller und FPGAS benötigen oft gleich mehrere, unterschiedliche Spannungen. Die Versorgung der Bauteile muss durch eine niederimpedante Anbindung erfolgen, für die eine möglichst homogene Powerlage benötigt wird. Zu schmale Versorgungsleitungen oder Einengungen durch viele Vias in den Versorgungsflächen führen zu Störungen. Ursprünglich hatte Altium ein Überprüfungstool für die „Power-Integrity-Analyse“ geplant, leider ist dieses nicht mit in dem Release erschienen. Bleibt zu hoffen, dass Altium es im nächsten Release bringen wird.

Advanced Layer Stack Manager

Mit dem „Multiple Layer Stack“ können die Lagenaufbauten für Sondertechnologien wie Flexible Leiterplatten oder auch Embedded Components definiert werden. Für die Highspeed-Anforderungen werden immer komplexere Lagenaufbauten erforderlich. Oft sind sogar mehrere unterschiedliche Leitungsimpedanzen auf einer Leiterplatte erforderlich, z. B. 60 Ohm Single ended und 100 Ohm differentielle Impedanz. Altium Designer bietet hier ein gutes Tool, mit dem die Planung und Dokumentation des Lagenaufbaus optimal durchgeführt werden kann. Das hilft dem Designer, die Verbindungen zu planen. Gleichzeitig dienen die Informationen dem Tool dazu, die Leitungslängen beim Lagenwechsel über die Z-Achse zu berechnen.

Mit dem „Multiple Layer Stack“ können die Lagenaufbauten für Sondertechnologien wie Flexible Leiterplatten oder auch Embedded Components definiert werden. Für die Highspeed-Anforderungen werden immer komplexere Lagenaufbauten erforderlich. Oft sind sogar mehrere unterschiedliche Leitungsimpedanzen auf einer Leiterplatte erforderlich, z. B. 60 Ohm Single ended und 100 Ohm differentielle Impedanz. Altium Designer bietet hier ein gutes Tool, mit dem die Planung und Dokumentation des Lagenaufbaus optimal durchgeführt werden kann. Das hilft dem Designer, die Verbindungen zu planen. Gleichzeitig dienen die Informationen dem Tool dazu, die Leitungslängen beim Lagenwechsel über die Z-Achse zu berechnen.

Highspeed-Design: Die Herausforderung an die Signalintegrität

Für die Signalübertragung der „Highspeed-Signale“, also Signale mit Anforderungen an eine schnelle Signalübertragung, gelten die gleichen Bedingungen wie zuvor bei den Speichern beschrieben. Hinzu kommen jedoch Designtechniken wie z. B. bei der LVDS-Technik, die mit einem Hin- und Rückleiter arbeitet. Dazu müssen die Leitungen parallel geführt werden und die gleiche Gesamtlänge aufweisen.

Die elektrischen Parameter, die für eine optimale Signalintegrität zu berücksichtigen sind, lauten:

- Timing = Kommt das Signal zur richtigen Zeit an? (Die Signalausbreitung (Laufzeit) auf der Leiterplatte beträgt ca. 140 Pikosekunden/25mm.)

- Signalintegrität = Wie sieht das Signal aus, wenn es ankommt?

- Noise = Störungen der Versorgungsspannung

Die im Bauteile-Datenblatt geforderten Impedanzen erfordern eine Kalkulation der Wellenwiderstände. Die Berechnung ist für jede Lage oder jedes Lagenpaar vorzunehmen, wenn die impedanzdefinierten Leitungen auf mehreren Lagen geführt werden. In die Berechnung fließen u. a. ein: die Leiterbreite, Leiterdicke sowie die Dicke und das ɛr des Dielektrikums. Hier bietet die Altium Version 15 ebenfalls Verbesserungen, wie z. B. beim „Tuning“ der Leitungen oder Leitungspaare. Pinpairs, Lengthtuning und Matching sind die Werkzeuge, die der Designer für solche Highspeed-Design benötigt. Das erspart aufwendige Handarbeit.

GED offizieller Betasite-Tester des neuen Altium Release

Neben den Highspeed-Funktionalitäten wurden in der Version 15 weitere neue Funktionen und Verbesserungen implementiert, darunter der IPC-2581-Standard und der Gerber-X2-Support für die Datenausgaben. GED war offiziell als Betasite-Tester bei den Vorprüfungen der endgültigen Altium Designer-Lizenz beteiligt und hatte so bereits frühzeitig Einblick in die neue Version. GED bietet den Premium-Layoutservice auf Altium Designer an, auch inklusive einer Highspeed-Simulation.

Highspeed-Simulation: Signal-Laufzeitberechnung ab 5 Gbit/sek

Ab Übertragungsraten im Bereich von 5 Gbit ist eine längenorientierte Betrachtung nicht mehr ausreichend genau genug. Dann muss die echte Signal-Laufzeitberechnung vorgenommen werden, wozu GED den leistungsfähigen SI-Simulator Hyperlynx einsetzt. Damit werden dann auch die Länge der Bonddrähte im Bauteil oder auch die Unterschiede der Lagen in der Leiterplatte mit in die Berechnung aufgenommen. Im Kintex-Datenblatt ist beim FB676-Gehäuse für die interne Verbindung zwischen Chip und Gehäuse ein möglicher Unterschied von 165 Pikosekunden ausgewiesen, das entspricht auf der Leiterplatte eine Leiterlänge von 20 mm. Das bedeutet, dass man für Highspeed-Elektronik der neuen Generation kaum noch ohne SI-Simulation auskommen wird.

Wollen Sie mehr erfahren?

Rufen Sie uns an – + 49 (0) 2247 92 19-0.

Oder senden Sie eine Nachricht.