FED-Regionalgruppe Düsseldorf diskutiert fertigungsgerechtes Design

Am 3. Dezember 2015 war die FED-Regionalgruppe Düsseldorf bei Ruwel International, einem führenden Leiterplattenhersteller, im niederrheinischen Geldern zu Gast. Das hochaktuelle Thema der Veranstaltung mit über 50 Teilnehmern war das fertigungsgerechte Leiterplattendesign: Wie lassen sich Fehler und Unklarheiten in den Fertigungsdaten minimieren, die Kosten reduzieren und die Termine einhalten? Welche Qualifikationen müssen Designer mitbringen, um die entsprechenden Anforderungen zu erfüllen? Organisiert hatte die Veranstaltung Hanno Platz, GED-Geschäftsführer und Leiter der FED-Regionalgruppe Düsseldorf.

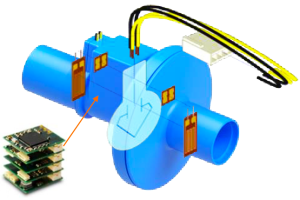

Neue Gehäuseformen und Mikrobauteile wie QFN (Quad Flat No Leads), CSP (Chip Scale Package) oder BTC (Bottom Terminated Components) haben einen weiteren Technologieschritt in der AVT ausgelöst – mit hohen Herausforderungen an das Design und die Fertigung. Die Problematik ist gut bekannt: Unklare Fertigungsdaten führen bei zunehmender Komplexität der Leiterplatten immer öfter zu Rückfragen des Herstellers und erfordern Nacharbeiten im Design oder schlimmer, Nacharbeit in der Baugruppenproduktion. Häufige Folgen sind Verzögerungen und Mehrkosten. Bekannt ist, dass der Leiterplattenhersteller produktionsbedingt Anpassungen der Daten vornehmen muss, um die Produzierbarkeit und Qualität sicherzustellen; Zunehmend modifizieren aber auch Leiterplattenhersteller die Daten, um Vereinfachungen in der Produktion zu erhalten. Das birgt freilich auch Risiken, wenn der Hersteller die elektrischen Eigenschaften der Schaltung verändert, ohne dass der Kunde davon weiß. Idealerweise erstellen Leiterplattendesigner also die Daten fertigungsgerecht optimiert, sodass der Hersteller nur noch toleranz- und produktionsbedingte Anpassungen vornehmen muss. Anders gesagt: Fertigungsoptimale Daten tragen entscheidend dazu bei, Rückfragen aus der Produktion zu reduzieren, Fehler zu eliminieren und Kosten zu minimieren.

Die Veranstaltungsvorträge befassten sich vor diesem Hintergrund mit den Fehlerquellen, der Optimierung der Leiterplatten- und Baugruppenfertigung und der Designerausbildung. In den Diskussionen ging es dann um konkrete Maßnahmen wie Tear-drops oder das „Non functional pad removal“ auf den Multilayer- Innenlagen.

Hanno Platz von GED und der Stellvertretende Regionalgruppenleiter, Hubert Kesternich, PCB-Designer bei Delphi Automotive, zeigten in ihren Vorträgen Beispiele für Fehler und Ausfälle in der Bestückung aufgrund mangelhafter Fertigungsdaten und benannten die Ursachen für die aktuell steigenden Unklarheiten in den Fertigungsdaten. Diese Ursachen liegen zum Teil auch in den CAD-Werkzeugen; Probleme resultieren beispielsweise aus Unzulänglichkeiten der automatischen Flächengenerierung mancher CAD-Tools. Die Referenten betonten die Rolle der Kommunikation und Abstimmung im Vorfeld der Produktion. Darüber hinaus legten sie dar, welche Möglichkeiten der Designer hat, um mit zusätzlichen CAD-Tools und Checklisten seine CAD- und Fertigungsdaten zu verifizieren.

Der Geschäftsführer der Ruwel International GmbH, Gerard van Dierendonck, präsentierte den aktuellen Stand des Hightech-Unternehmens und die Geschichte von Ruwel: eine spannende Schilderung, wie in den letzten Jahren das gesamte Unternehmen umgebaut wurde – vom High Volume/Low Mix-Produzenten mit zwei Großkunden zu dem flexiblen High Mix/Low Volume-Fertiger mit 20 Kunden von heute. Im Werk Geldern mit einer Produktionsfläche von 21.000 qm sind durch Automatisierung in den drei Schichten nur noch 235 Mitarbeiter beschäftigt. Dazu waren umfangreiche Investitionen in neue Maschinen und Anlagen erforderlich, die aktuell eine jährliche Produktionskapazität von 400.000 qm Außenlagen und von 1,2 Mio. qm Innenlagen ermöglichen. Hauptsächlich werden High-End-Leiterplatten produziert, wie HF, HDI und Hochstrom-LP.

Ruwel ist einer der traditionsreichsten Leiterplattenhersteller in Europa. Das von Fritz Stahl 1945 ursprünglich in Berlin gegründete Unternehmen produziert seit 1956 in Geldern als erstes Unternehmen in Europa Leiterplatten unter Serienbedingungen. Seit 2011 gehört Ruwel zur Unimicron Group – einem der Weltmarktführer in der Leiterplattenbranche mit 14 Werken in Asien und einem Jahresumsatz von fast 2,5 Milliarden USD.

Im nächsten Fachvortrag präsentierte Oliver Holz, Leiter Produktmanagement bei Ruwel International, „Kosteneffizientes und fertigungsgerechtes Leiterplattendesign“ aus Sicht des Herstellers. Die optimale Auslastung der Produktionspanel hat großen Einfluss auf die Stückkosten. Manchmal sind es nur ein paar Millimeter, die eine Verteuerung der Stückkosten von über 20 % ausmachen können. Holz betonte, dass der steigende Kosten- und Zeitdruck keine „Design-Sünden“ mehr erlaube. Dabei könnten bereits kleine Änderungen im Design große Fehler verhindern und spürbar Kosten reduzieren. Eine frühzeitige Abstimmung mit der Fertigung ist wichtig. Dazu gab er ganz konkrete Tipps aus Herstellersicht zur Optimierung von Design und Fertigungsdaten. Für seine Kunden hat Ruwel einen 136-seitigen Tischreiter in digitaler Form erstellt, der freundlicherweise auch den Teilnehmern der FED-Veranstaltung zur Verfügung gestellt wurde.

Zum Abschluss der Veranstaltung nutze der neue FED-Geschäftsführer Jörg Meyer, der seinen Antrittsbesuch in der Regionalgruppe absolvierte, die Möglichkeit, über die Relevanz der Ausbildung und Qualifikation des Designers zu sprechen. Das Leiterplattendesign ist inzwischen so umfangreich und wichtig geworden, weil es unmittelbar Einfluss auf die Zuverlässigkeit, die Qualität und die Kosten der Elektronikprodukte hat. Um dem gerecht zu werden, hat der FED ein komplett neues, erweitertes Ausbildungskonzept für den „Zertifizierten Elektronik Designer“ (ZED) entwickelt. Der fünfstufige Schulungskurs setzt auf den CID des IPC auf, steigt aber tiefer in die Themen ein und ist technologisch weiterführender. Der FED trägt damit der Anforderung Rechnung, dass Designer heute unter anderem über fundierte und praxisnahe Kenntnisse über Materialien, Fertigungsprozesse, Toleranzketten und die Footprintgestaltung verfügen müssen. Nach erfolgreichem Abschluss tragen die Teilnehmer die wertvolle Qualifikation des „ZED“.

Zum Abschluss der Veranstaltung nutze der neue FED-Geschäftsführer Jörg Meyer, der seinen Antrittsbesuch in der Regionalgruppe absolvierte, die Möglichkeit, über die Relevanz der Ausbildung und Qualifikation des Designers zu sprechen. Das Leiterplattendesign ist inzwischen so umfangreich und wichtig geworden, weil es unmittelbar Einfluss auf die Zuverlässigkeit, die Qualität und die Kosten der Elektronikprodukte hat. Um dem gerecht zu werden, hat der FED ein komplett neues, erweitertes Ausbildungskonzept für den „Zertifizierten Elektronik Designer“ (ZED) entwickelt. Der fünfstufige Schulungskurs setzt auf den CID des IPC auf, steigt aber tiefer in die Themen ein und ist technologisch weiterführender. Der FED trägt damit der Anforderung Rechnung, dass Designer heute unter anderem über fundierte und praxisnahe Kenntnisse über Materialien, Fertigungsprozesse, Toleranzketten und die Footprintgestaltung verfügen müssen. Nach erfolgreichem Abschluss tragen die Teilnehmer die wertvolle Qualifikation des „ZED“.

Zum späten Nachmittag erhielten die FED-Gäste die Möglichkeit zur Werksbesichtigung. Die komplette Runde wurde in mehreren Gruppen durch die beiden Werke geführt, die sich hauptsächlich in Innenlagen- und Außenlagenfertigung aufteilen. Der anderthalbstündige Rundgang verdeutlichte, mit wie wenig Personal die moderne, hochautomatisierte Leiterplattenproduktion auskommt. Beeindruckend waren die neuesten Maschinen und Anlagen wie Galvanik, Ätzanlagen und Prüftechnik, für die in den letzten zwei Jahren hohe Investitionen vorgenommen wurden.

Insgesamt war es ein sehr konstruktiver und ertragreicher Tag bei Ruwel. Beide Seiten, Design und Fertigung, konnten vom der Austausch der Ideen und des Know-hows profitieren.

Hanno Platz verabschiedete die Teilnehmer mit guten Wünschen für eine schöne Weihnachtszeit und dem Hinweis auf Termine für 2016. Am 3.3.2016 gibt es eine Sonderveranstaltung zur Besichtigung der Ford-Werke in Köln und am 13.4. die RGD-Sitzung zum Thema 3D-Elektronik-Lösungen mit Vorträgen seitens der Firmen Würth und GED. Details dazu werden in den Einladungen noch frühzeitig mitgeteilt.

Wollen Sie mehr zum fertigungsgerechten Design made by GED erfahren?

Rufen Sie uns an – + 49 (0) 2247 92 19-0.

Oder senden Sie eine Nachricht.